$INTC $AMD | CPU指令集架構—ARM、x86與RISC-V 的的百年戰局

黃仁勳點出的重點:Installed Base 決定一切,x86 生態護城河又深又廣!

前言:最近由Agentic AI 帶旺了CPU 需求,令Intel 及AMD 股價大漲,加上一直想重新梳理關於ARM 及 x86 的兢爭狀態,同時也好奇去年黃仁勳一直掛在咀邊,探用GB10 的N1X 怎麼忽然沒戲了,因此重新研究了關於CPU 及ISA 兢爭的課題,希望對讀者有幫助。

運算架構的底層邏輯:x86、ARM與RISC-V的技術深度對比

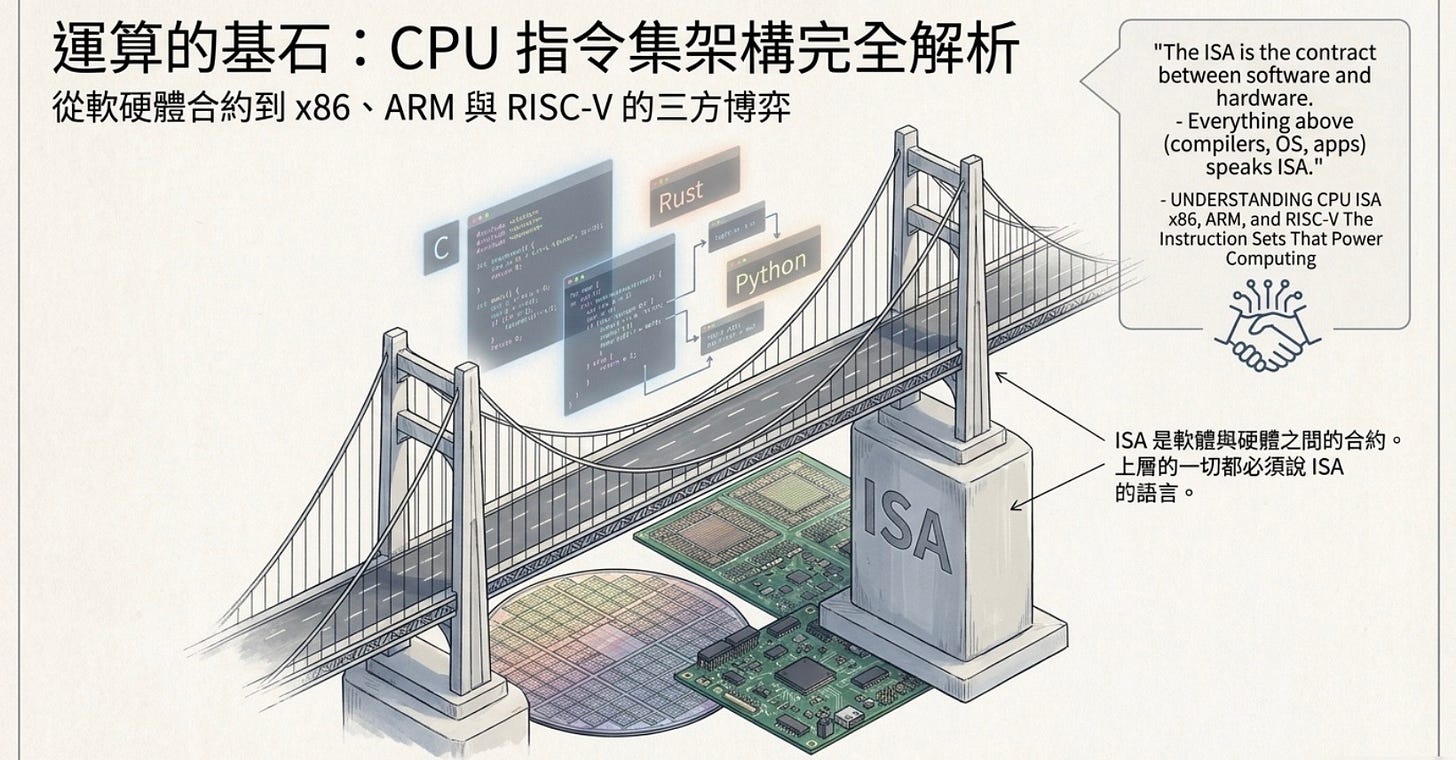

在當今全球半導體產業的激烈博弈中,尤其進入AI Agentic 世代,中央處理器(CPU)再次成為主角,本篇文章我們深入探討一下CPU 底層的指令集架構(Instruction Set Architecture, ISA),它不僅是硬體設計的藍圖,更是決定軟體生態、商業模式與未來人工智慧(AI)運算效率的核心基礎。

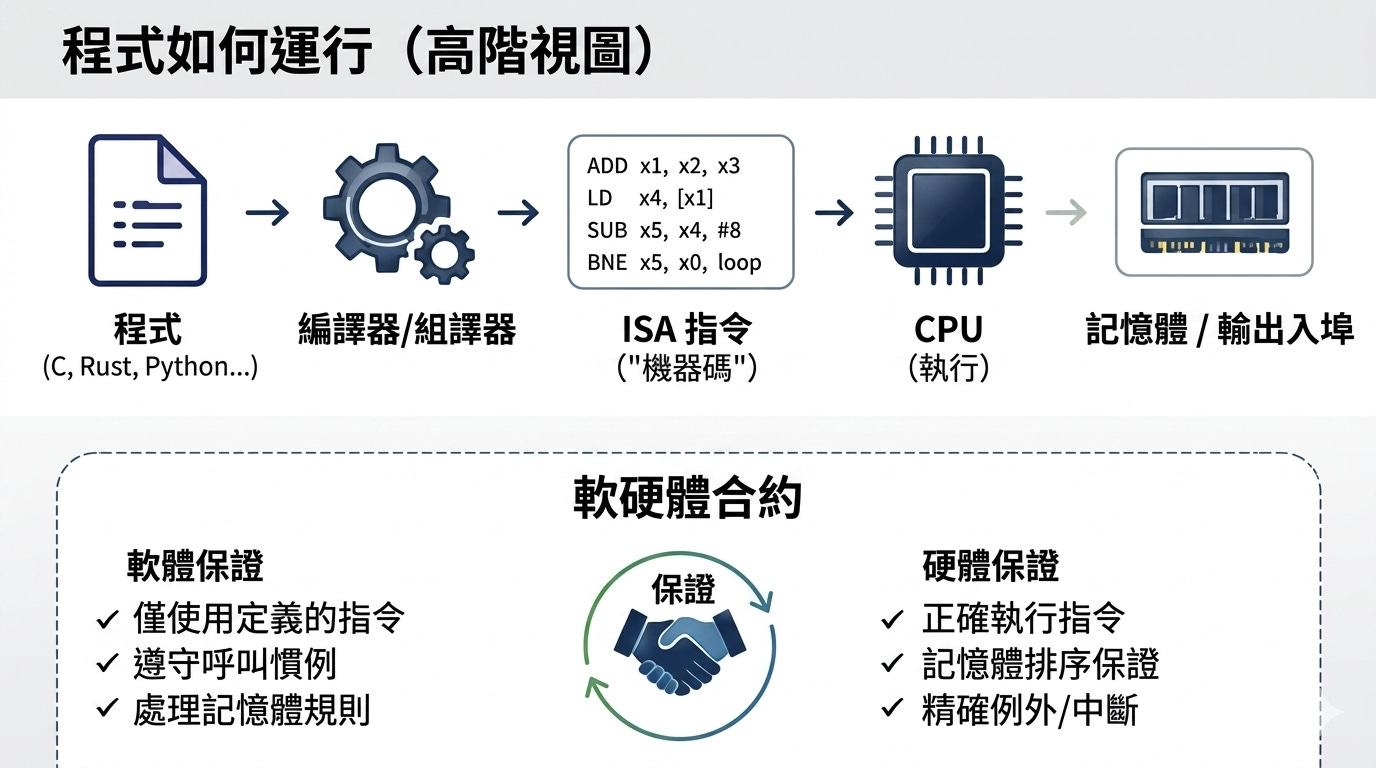

什麼是指令集架構 (ISA)?

ISA 是軟體與硬體之間的「合約」,一切軟體(編譯器、作業系統、應用程式)都必須透過 ISA 來與硬體溝通 。軟體保證僅使用已定義的指令並遵守記憶體規則;硬體則保證正確執行指令、維持記憶體排序及精確處理例外情況 。

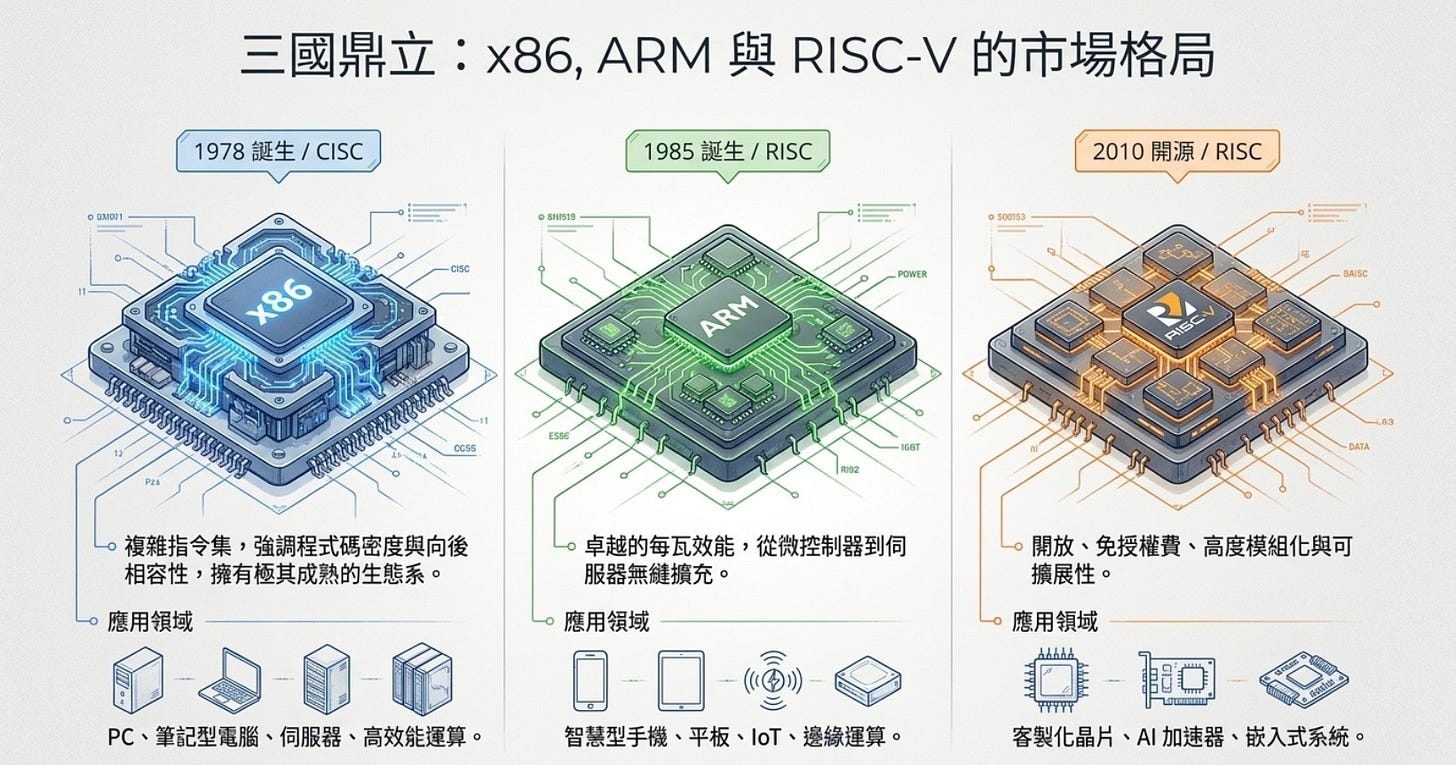

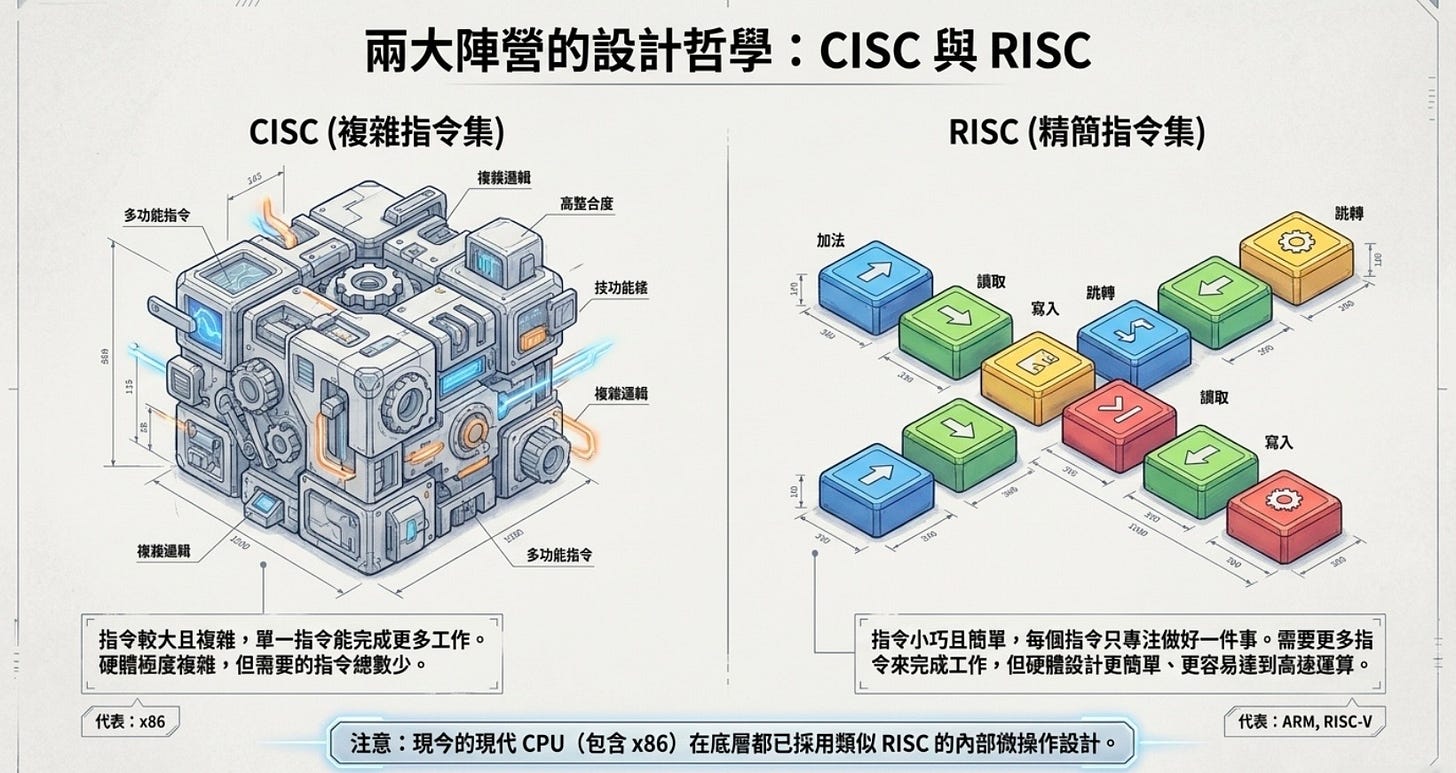

當前主導市場的三大架構—代表複雜指令集(CISC)的x86、代表精簡指令集(RISC)的ARM,以及主打完全開源與模組化的新興標準RISC-V—在設計哲學上存在著根本性的分歧。這些技術層面的差異,深刻影響了它們在不同運算場景下的能耗比、絕對效能以及生態系統的延展性。

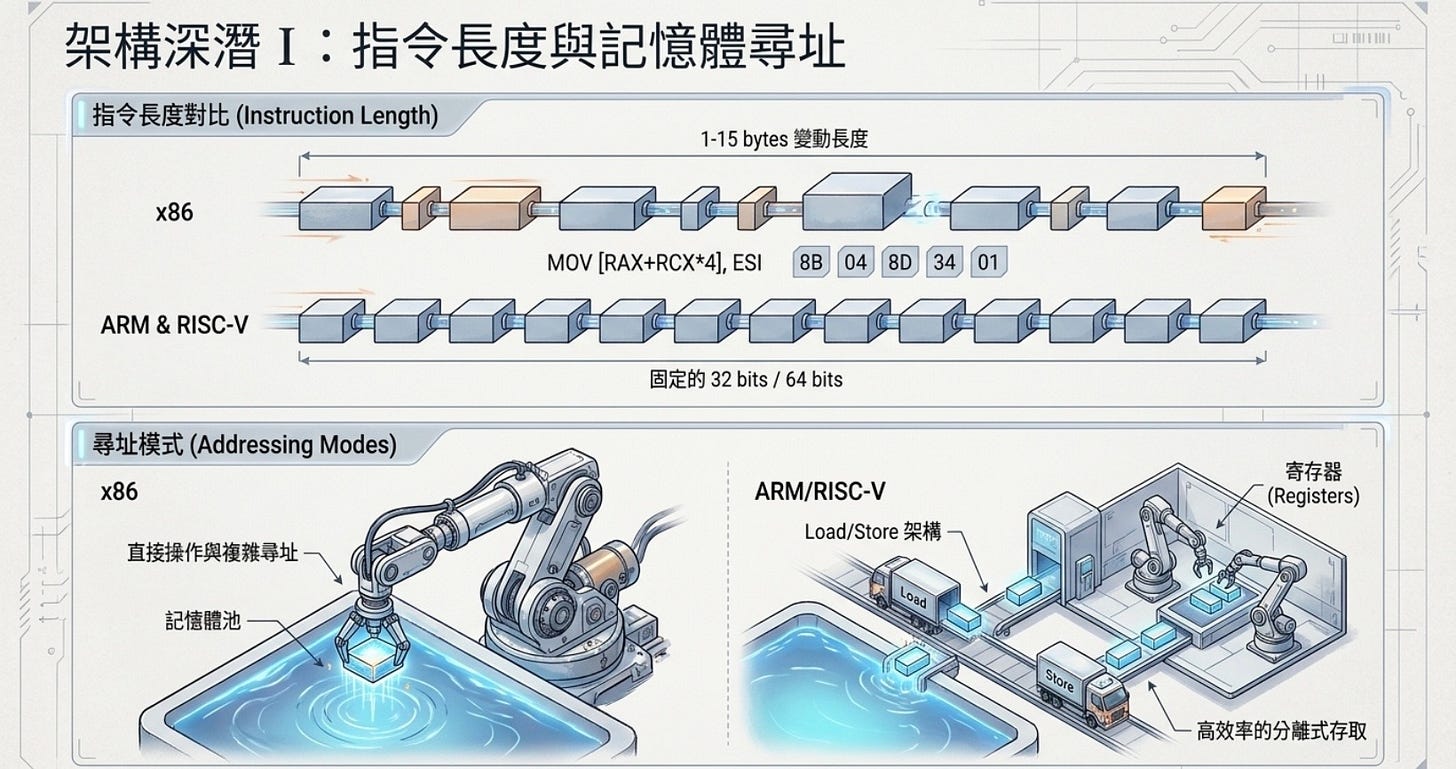

x86架構的歷史包袱與效能極限,源自於近50 年前為了在記憶體極其昂貴的時代最小化程式碼長度,而採用的 Variable-length instructions 設計 。在這種架構下,處理器在讀取指令之前無法預知指令的邊界,導致其必須依賴複雜的硬體解碼器(Instruction Decoders)來進行多步驟的動態解析 。這種複雜的解碼邏輯不僅佔據了大量寶貴的矽晶圓面積,更在Superscalar 同時執行多條指令時產生了顯著的功耗。

ARM架構徹底貫徹了RISC的設計哲學,指令解碼器極度簡化,處理器不再需要耗費大量電晶體來猜測指令長度與解析複雜指令。釋放出來的晶片面積與功耗,讓晶片設計者得以配置更多的物理核心、更大容量的L3快取,或是整合強大的神經網絡處理單元(NPU) 。這種硬體層面的極致簡化,使得ARM架構在行動裝置與強調總體擁有成本(TCO)的雲端資料中心中具備了難以匹敵的先天優勢。

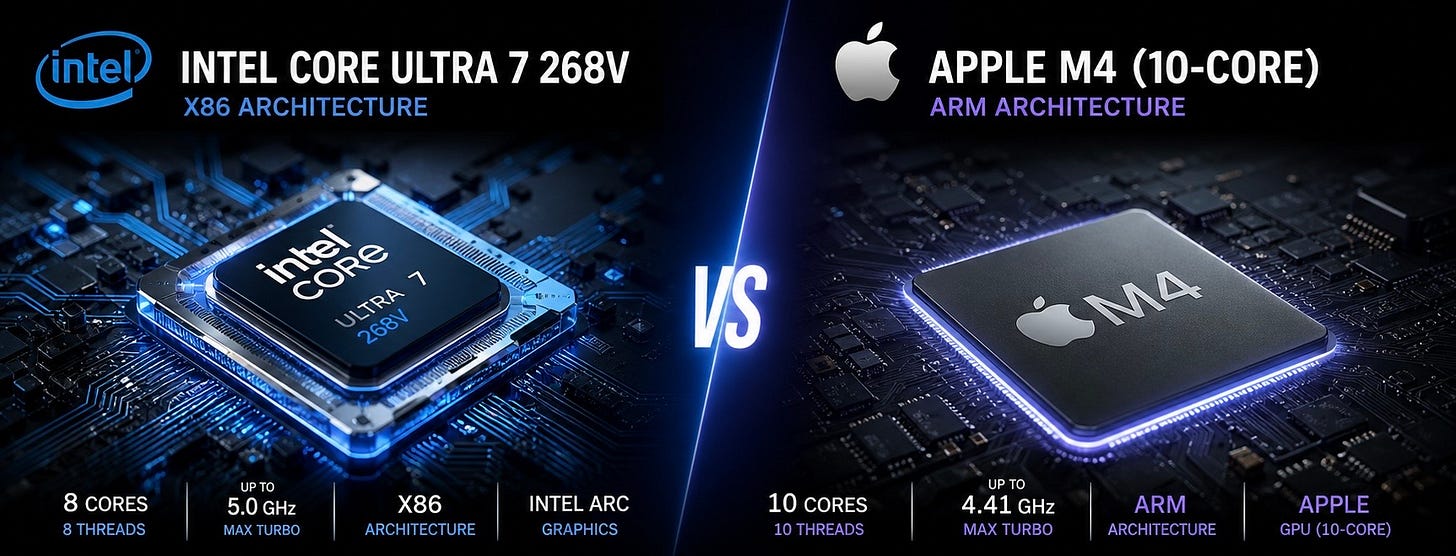

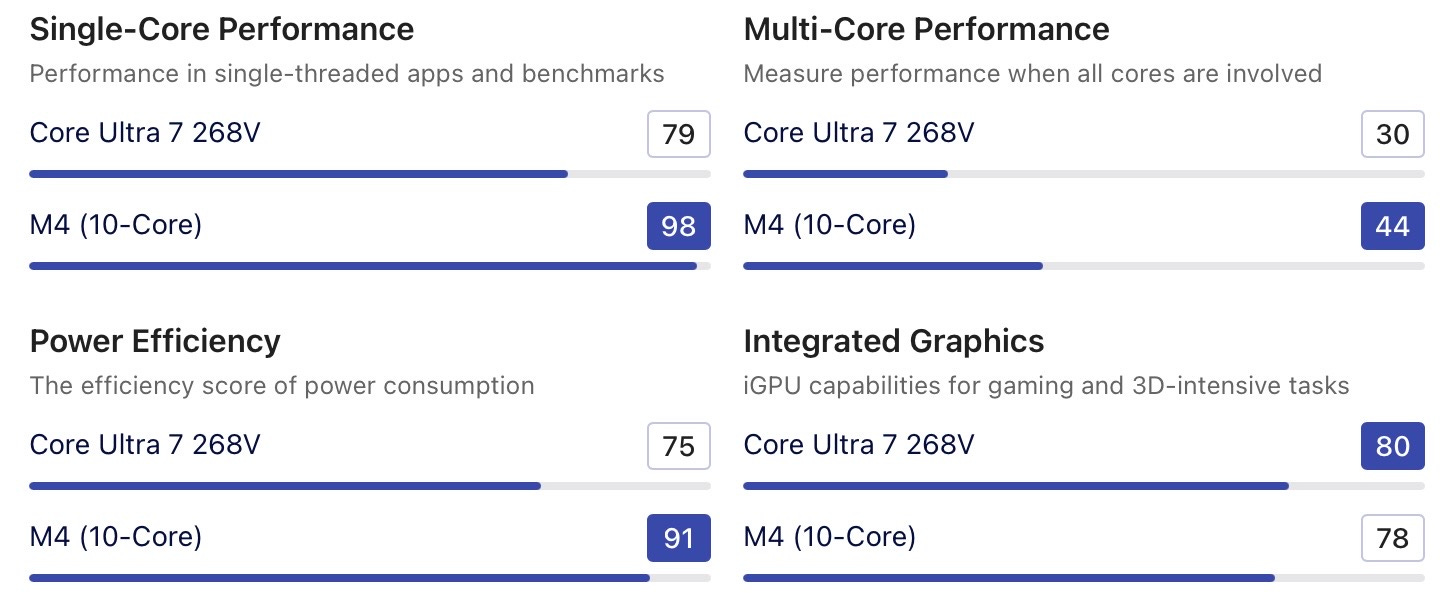

我挑選了比較新款及可比性最佳的兩款產品來作分析,M4 (ARM) 除了在圖像處理小幅落後外,其他方面都完勝x86 代表,也難怪最近養龍蝦熱,搶的都是Apple Mini,跑的就是M4。

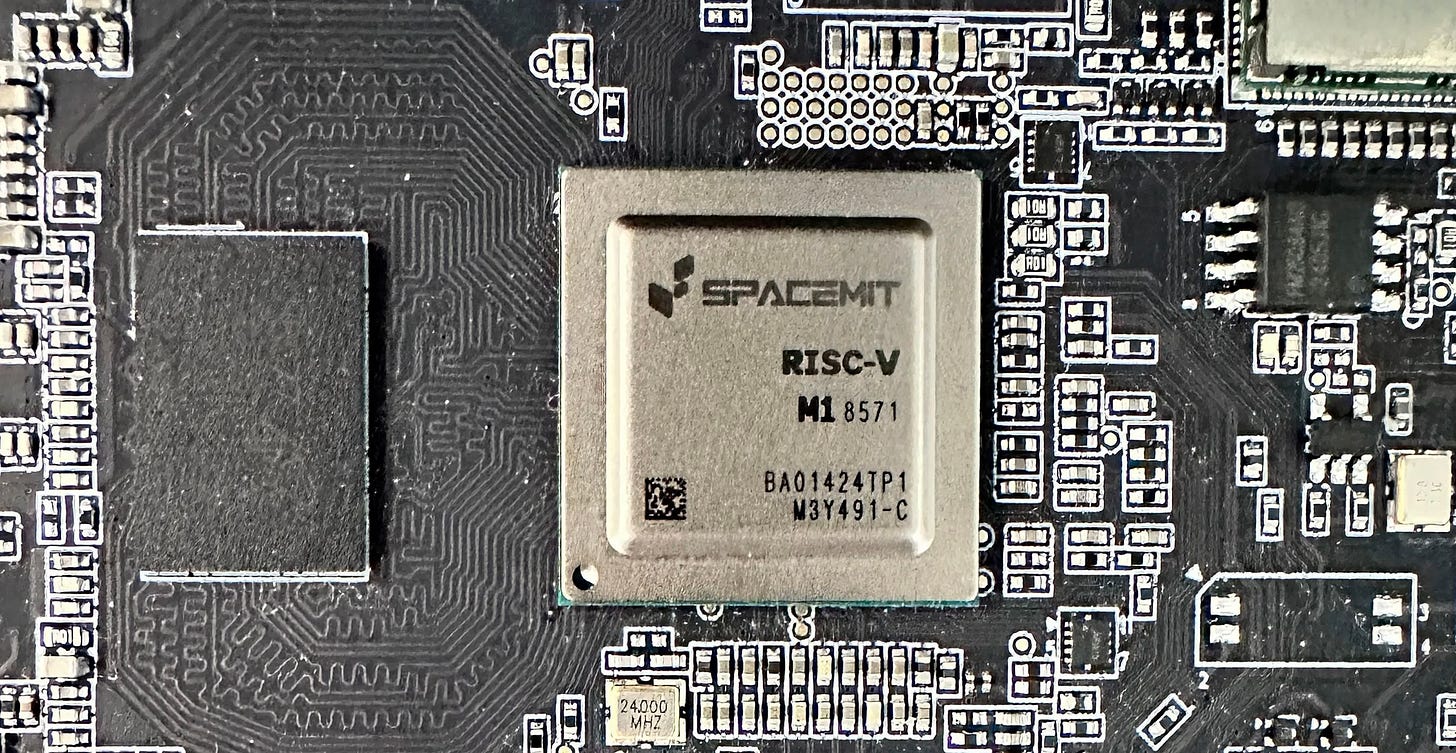

RISC-V則是這場架構戰爭中的顛覆性力量。作為一個完全開放標準(Open Standard)的ISA,RISC-V徹底消除了x86的雙頭壟斷與ARM高昂的專有授權版稅(Royalty-free) 。RISC-V的核心技術優勢在於其「凍結的基礎指令集」(Frozen Base)與極致的模組化擴充能力 。中國目前正在大舉投資RISC-V,希望擺脫西方壟斷。

x86與ARM在數十年的發展中,為了維持向後相容性,累積了數以千計的冗餘指令,導致現代處理器中存在大量平時極少使用的「暗矽」(Dark Silicon),白白浪費了靜態功耗 。相反地,RISC-V的基礎整數指令集僅包含不到五十條核心指令,為晶片設計提供了最輕量化的基礎 。在此之上,企業可以透過自定義擴充指令(Custom Extensions)將專用的AI加速邏輯直接寫入CPU。

目前 RISC-V更標準化了向量擴充(Vector Extensions, RVV),這使其在處理大型語言模型(LLM)推論與複雜矩陣乘法時,展現出比更具彈性的效能 。目前,RISC-V在車用電子、邊緣AI與物聯網領域的市場滲透率已提前突破25% ,且根據SHD Group的預測,其市佔率將從2021年的2.5%暴增至2031年的33% 。

ARM的架構優勢為何無法轉化為PC與通用伺服器市場的絕對勝利?

儘管ARM架構在實驗室的能效測試中展現出碾壓x86的數據,且在雲端超大規模資料中心(如AWS Graviton4實例)中證明了能帶來高達40%至60%的能源節省與20%的成本降低 ,但ARM架構在通用個人電腦(PC)與企業級伺服器市場的擴張卻始終處於被動。